# eMac Developer Note

**Hardware & Drivers > Apple Hardware**

#### ď

Apple Inc.

© 2001, 2003 Apple Computer, Inc.

All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Inc., with the following exceptions: Any person is hereby authorized to store documentation on a single computer for personal use only and to print copies of documentation for personal use provided that the documentation contains Apple's copyright notice.

The Apple logo is a trademark of Apple Inc.

Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws

No licenses, express or implied, are granted with respect to any of the technology described in this document. Apple retains all intellectual property rights associated with the technology described in this document. This document is intended to assist application developers to develop applications only for Apple-labeled computers.

Every effort has been made to ensure that the information in this document is accurate. Apple is not responsible for typographical errors.

Apple Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010

Apple, the Apple logo, AirPort, AirPort Extreme, eMac, FireWire, Mac, Mac OS, Macintosh, QuickTime, SuperDrive, and Velocity Engine are trademarks of Apple Inc., registered in the United States and other countries.

DEC is a trademark of Digital Equipment Corporation.

OpenGL is a registered trademark of Silicon Graphics, Inc.

PowerPC and and the PowerPC logo are trademarks of International Business Machines Corporation, used under license therefrom.

Simultaneously published in the United States and Canada.

Even though Apple has reviewed this document, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS DOCUMENT IS PROVIDED "AS IS," AND YOU, THE READER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS DOCUMENT, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# Contents

| Introduction | Introduction to eMac Developer Note 9 |  |  |

|--------------|---------------------------------------|--|--|

|              | Organization of This Document 9       |  |  |

| Chapter 1    | Overview to the eMac 11               |  |  |

|              | New Features 11                       |  |  |

|              | All Features 11                       |  |  |

|              | External Features 12                  |  |  |

|              | System Software 13                    |  |  |

|              | Computer Identification 13            |  |  |

|              | NMI without Programmer's Switch 13    |  |  |

|              | Velocity Engine Acceleration 14       |  |  |

| Chapter 2    | Architecture 15                       |  |  |

|              | Block Diagram and Buses 15            |  |  |

|              | Block Diagram 15                      |  |  |

|              | Main ICs and Buses 16                 |  |  |

|              | Microprocessor and Cache 17           |  |  |

|              | PowerPC G4 Microprocessor 17          |  |  |

|              | Level 2 Cache 17                      |  |  |

|              | Uni-N Bridge and Memory Controller 17 |  |  |

|              | Processor Bus 17                      |  |  |

|              | Main Memory Bus 18                    |  |  |

|              | Accelerated Graphics Port Bus 18      |  |  |

|              | Video Display Subsystem 18            |  |  |

|              | PCI Bus 19                            |  |  |

|              | Boot ROM 19                           |  |  |

|              | Ethernet Controller 19                |  |  |

|              | FireWire 400 Controller 19            |  |  |

|              | KeyLargo I/O Controller 20            |  |  |

|              | DMA Support 20                        |  |  |

|              | Interrupt Support 20                  |  |  |

|              | USB Interface 20                      |  |  |

|              | Ultra DMA Data Transfer 21            |  |  |

|              | Enhanced IDE Interface 21             |  |  |

|              | Modem Slot Support 21                 |  |  |

|              | Wireless LAN Module 21                |  |  |

|              | Sound Circuitry 22                    |  |  |

|              | Power Controller 22                   |  |  |

## **Devices and Ports 23** Chapter 3 USB Ports 23 USB Connectors 23 USB Features 24 FireWire 400 Ports 24 FireWire 400 Device Programming 25 FireWire 400 Connector 25 Target Disk Mode 26 Ethernet Port 27 Internal Modem 27 AirPort Extreme Card 28 Data Security 28 AirPort Extreme Hardware 28 AirPort Extreme Software 29 Hard Disk Drive 29 CD-ROM Drive 29 Combo Drive DVD-ROM/CD-RW 29 SuperDrive DVD-R/CD-RW Drive 30 Video Display 31 External Display Port 31 Video Display Connector 32 Older Monitors Not Supported 33 Keyboard 33 Keyboard Features 33 Keyboard Layout 34 MultiMedia Control Keys 34 Keyboard and USB 34 Mouse 35 Sound System 35 Sound Inputs 35 Sound Outputs 36 Sound Specifications 37 RAM Expansion 39 Chapter 4 RAM Expansion Slots 39 RAM Expansion Modules 39 Mechanical Design of RAM DIMMs 39 Electrical Design of RAM DIMMs 40 Appendix A **Supplemental Reference Documents 43** Apple Technical Notes 43 3D Graphics 43

PowerPC G4 Microprocessor 43

### **CONTENTS**

Velocity Engine (AltiVec) 44

Mac OS X 44

I/O Kit 44

Open Firmware 44

RAM Expansion Modules 45

ATA Interface 45

USB Interface 46

FireWire Interface 46

Wireless Networks 46

### Appendix B Abbreviations 47

# Figures and Tables

| Chapter 2  | Architecture 15      |                                                                   |  |  |

|------------|----------------------|-------------------------------------------------------------------|--|--|

|            | Figure 2-1           | Block diagram 16                                                  |  |  |

| Chapter 3  | Devices and Ports 23 |                                                                   |  |  |

|            | Figure 3-1           | USB Type A port and pins 23                                       |  |  |

|            | Figure 3-2           | FireWire 400 connector 25                                         |  |  |

|            | Figure 3-3           | Video display connector 32                                        |  |  |

|            | Figure 3-4           | ANSI keyboard layout 34                                           |  |  |

|            | Table 3-1            | Signals on the USB port 23                                        |  |  |

|            | Table 3-2            | Signals on the FireWire 400 connector 25                          |  |  |

|            | Table 3-3            | Signals on the Ethernet connector 27                              |  |  |

|            | Table 3-4            | Types of media read and written by the Combo drive 30             |  |  |

|            | Table 3-5            | Types of media read and written by the SuperDrive 30              |  |  |

|            | Table 3-6            | Display resolutions and pixel depths 31                           |  |  |

|            | Table 3-7            | Display adapters 31                                               |  |  |

|            | Table 3-8            | Video signals for a VGA display 32                                |  |  |

|            | Table 3-9            | Video signals for a TV display 32                                 |  |  |

|            | Table 3-10           | Distortion specifications 37                                      |  |  |

|            | Table 3-11           | SNR specifications 37                                             |  |  |

| Chapter 4  | RAM Expa             | nsion 39                                                          |  |  |

|            | Table 4-1            | Sizes of RAM expansion devices and DIMMs 40                       |  |  |

|            | Table 4-2            | Address multiplexing modes for SDRAM devices 41                   |  |  |

| Appendix B | Abbreviati           | ions 47                                                           |  |  |

|            | Table B-1            | Standard units of measure used in this developer note include: 47 |  |  |

|            | Table B-2            | Other abbreviations used in this note include: 47                 |  |  |

# Introduction to eMac Developer Note

This developer note gives a technical description of the eMac. The note provides information about the computer's internal design, input-output features, and expansion capabilities.

This developer note is intended to help hardware and software developers design products that are compatible with the products described here. If you are not already familiar with Macintosh computers or if you would simply like additional technical information, refer to Appendix A, "Supplemental Reference Documents," (page 43) for details.

# Organization of This Document

The information in this note is arranged in four chapters and two appendixes.

- Chapter 1, "Introduction", (page 11) introduces the eMac, describes its features, and mentions a few software issues of interest to developers.

- Chapter 2, "Architecture", (page 15) describes the internal organization of the computer. It includes a functional block diagram and descriptions of the main components on the logic board.

- Chapter 3, "Devices and Ports", (page 23) describes the I/O ports and the built-in I/O devices.

- Chapter 4, "RAM Expansion", (page 39) includes development guidelines for the RAM expansion modules.

- Appendix A, "Supplemental Reference Documents", (page 43) provides sources of additional information about the technologies used in the eMac.

- Appendix B, "Abbreviations", (page 47) lists standard units of measure and other abbreviations used in this developer note.

### INTRODUCTION

Introduction to eMac Developer Note

# Overview to the eMac

This chapter lists the features of the eMac and provides information about a few software issues of interest to developers.

## **New Features**

The features that have changed are listed here with links to the sections that describe them.

- Microprocessor: The eMac has a PowerPC G4 microprocessor running at a clock speed of 1 GHz. For more information, see "PowerPC G4 Microprocessor" (page 17).

- Hard disk storage: The built-in hard disk drive has a capacity of 40 GB or 80 GB. Some configurations have 80 GB and 160 GB build-to-order options. For more information, see "Hard Disk Drive" (page 29).

### **All Features**

Here is a complete list of the features of the eMac. Each feature is described in more detail in a later section.

- Microprocessor: The eMac has a PowerPC G4 microprocessor running at a clock speed of 1 GHz. For more information, see "PowerPC G4 Microprocessor" (page 17).

- Main memory bus: The speed of the memory bus is 133 MHz. For more information, see "Main Memory Bus" (page 18).

- Cache: The 256 KB backside L2 cache is included on the microprocessor IC and has the same clock speed as the microprocessor. For more information, see "Level 2 Cache" (page 17).

- Memory: The eMac comes with 128 or 256 MB of PC133 SDRAM installed in one of two standard 168-pin DIMM expansion slots. The RAM slots can support up to 512 MB each for a maximum total of 1 GB. For more information, see "RAM Expansion Modules" (page 39).

- Hard disk storage: The built-in hard disk drive has a capacity of 40 GB or 80 GB. Some configurations have 80 GB and 160 GB build-to-order options. For more information, see "Hard Disk Drive" (page 29).

- CD-ROM drive: One configuration has a CD-ROM drive. For more information, see "CD-ROM Drive" (page 29).

- Combo DVD-ROM/CD-RW drive: One configuration has a combination DVD-ROM/CD-RW drive. For more information, see "Combo Drive DVD-ROM/CD-RW" (page 29).

- SuperDrive (CD-RW/DVD-R): One configuration has a SuperDrive (CD-RW/DVD-R). For more information, see "SuperDrive DVD-R/CD-RW Drive" (page 30).

- External video monitor: The mini-VGA display connector supports VGA, composite, and S-video formats for devices such as monitors, projectors, and television sets. A video adapter with composite and S-video connectors is available separately. For more information, see "External Display Port" (page 31).

11 **New Features**

- **Graphics acceleration:** The video circuits provide built-in 2D and 3D acceleration using Radeon 7500 IC with 32 MB 180 MHz DDR memory. For more information, see "Video Display Subsystem" (page 18).

- Video RAM: The video hardware includes 32 MB of DDR video memory, which supports 3D features and millions of colors in all resolutions. For more information, see "Video Display Subsystem" (page 18) and "Video Display" (page 31).

- **USB ports:** The eMac has three USB 1.1 ports on the main chassis and two more on the keyboard. For more information, in "USB Ports" (page 23).

- **FireWire 400 ports:** The eMac has two IEEE-1394a FireWire 400 ports, which support transfer rates of 100, 200, and 400 Mbps. For more information, see "FireWire 400 Ports" (page 24).

- Target Disk Mode: The computer can act like a FireWire storage device connected to another computer. See "Target Disk Mode" (page 26).

- Modem: Some models have a built-in V.92 fax modem with a 56 Kbps data rate. For more information, see "Internal Modem" (page 27).

- **Ethernet:** The eMac has a built-in Ethernet port for a 10Base-T and 100Base-TX operation. For more information, see "Ethernet Port" (page 27).

- AirPort Extreme Card: An internal AirPort Extreme Card wireless LAN module is available as a build-to-order option or as a user-installable upgrade. For more information, see "AirPort Extreme Card" (page 28).

- **Sound:** The eMac has a built-in microphone, stereo speakers with amp, a line-level stereo input jack, and a stereo headphone jack. For more information, see "Sound System" (page 35).

- **Keyboard:** The eMac comes with an Apple Keyboard. The keyboard is also a USB hub with two USB ports. For more information, see "Keyboard" (page 33).

- **Mouse:** The computer comes with an Apple Mouse, a USB mouse with optical tracking. For more information, see "Mouse" (page 35).

- Size and weight: The eMac is 40.6 cm (15.8 inches) high, 40.6 cm (15.8 inches) wide, and 40.7 cm (15.9 inches) deep; it weighs 22.7 kg (50.0 pounds).

- **Display:** The eMac has a built-in 17-inch flat color CRT monitor with a 16-inch viewable diagonal. For more information, see "Video Display" (page 31).

## **External Features**

The eMac is housed in a polycarbonate plastic enclosure that includes the display. The separate keyboard and mouse are also designed in polycarbonate plastic.

The front of the enclosure is dominated by the 17 inch flat display. The front also includes, below the display, the following features:

- Center-positioned, tray-loading CD-ROM, Combo drive, or SuperDrive

- Access to AirPort Extreme Card slot

- Stereo speakers, one on either side

- Power-on light, located near the speaker on the right side; the light has a steady white glow when on; it pulses in sleep mode

Overview to the eMac

■ Built-in microphone

The right side of the enclosure, as viewed from the front, contains the I/O panel. The I/O panel contains the following features:

- Two FireWire 400 ports

- Modem connector (on the models that have an internal modem)

- Ethernet port

- Three USB ports

- Video monitor connector (mini-VGA)

- Headphone jack

- Sound-in jack

The receptacle for the power cord is located on the back. The back panel also includes the following features:

- Power button

- Kensington security slot

The back portion of the bottom of the enclosure has a door that can be opened for access to the expansion RAM. For more information, see "RAM Expansion Slots" (page 39).

# System Software

The eMac comes with Mac OS X version 10.3 or later installed as the default system. Mac OS 9 applications can be run in Classic mode. For more information about Mac OS X, see the reference listed in "Mac OS X" (page 44).

# Computer Identification

Rather than reading the box flag or the model string and then making assumptions about the computer's features, applications that need to find out the features of the computer should use IORegistry calls to test for the features they require. IORegistry calls are part of the I/O Kit API. For more information, see the references listed at "I/O Kit" (page 44).

Asset management software that reports the kind of computer it is run on can obtain the value of the model property from the IOService plane of the IORegistry. For the eMac, the value of the string in the compatible property is PowerMac4, 4.

# NMI without Programmer's Switch

Current Macintosh computers do not have a programmer's switch, which allowed users to generate a non-maskable interrupt (NMI). The paragraphs below describe how to generate an NMI from a remote session for systems that do not have a physical programmer's switch.

#### **CHAPTER 1**

Overview to the eMac

Starting with Mac OS X 10.1.2, the OS will promote and recognize the DB\_NMI bit in the "bootargs" property of the "chosen" node from Open Firmware. When the DB\_NMI bit is set, the user can generate a non-maskable interrupt (NMI) by pressing the system's power button. This replaces the power button's sleep or wake response. The system reads the state of the bit at boot time from the boot - args configuration variable. For more information about the debug flags, please see *Inside Mac OS X: Kernel Programming*.

To set the DB\_NMI bit, enter the following command at the Terminal to display the current debug flag settings.

```

% nvram boot-args

```

Add the parameter debug=0x4, as follows.

```

% sudo nvram boot-args="<current settings> debug=0x4"

```

Once the DB\_NMI bit is set, reboot the machine by pressing the power button for approximately 3 seconds, thus generating an NMI.

Note: If the power button is pressed for more than five seconds, the system will immediately power off.

The power button will retain this functionality until Mac OS X is restarted without the DB\_NMI bit set. To clear this bit, issue the nvram command omitting debug=0x4 parameter,, as follows.

```

% sudo nvram boot-args=""

```

**Note:** The debug flags bit will be cleared if you use System Preferences to change the startup disk. It may also be cleared if you perform an installation that requires a restart.

## **Velocity Engine Acceleration**

The Velocity Engine (an implementation of AltiVec) is the vector processing unit in the PowerPC G4 microprocessor. Some system software has been modified to take advantage of the accelerated processing that the Velocity Engine makes possible. System software has also been modified to support low-level operations using the Velocity Engine.

For complete information on the Velocity Engine, refer to the following Apple website:

http://developer.apple.com/hardwaredrivers/ve/index.html

This chapter describes the architecture of the eMac. It includes information about the major components on the main logic board: the microprocessor, the other main ICs, and the buses that connect them to each other and to the I/O interfaces.

# **Block Diagram and Buses**

This section is an overview of the major ICs and buses on the computer's main logic board.

# **Block Diagram**

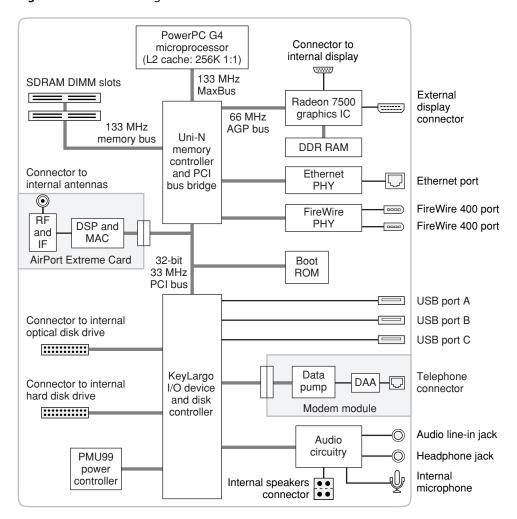

Figure 2-1 (page 16) is a simplified block diagram of the main logic board. The diagram shows the main ICs and the buses that connect them together.

Figure 2-1 Block diagram

### Main ICs and Buses

The architecture of the eMac is designed around the PowerPC G4 microprocessor and and two custom ICs: the Uni-N memorycontroller and bus bridge and the KeyLargo I/O controller.

The eMac has four major buses.

- processor bus: 133 MHz, 64-bit bus connecting the processor module to the Uni-N IC

- memory bus: 133 MHz, 64-bit bus connecting the main memory to the Uni-N IC

- AGP bus: 66 MHz, 32-bit bus connecting the AGP card to the Uni-N IC

- PCI bus: 33 MHz, 32-bit bus connecting the boot ROM and AirPort Extreme module to the KeyLargo I/O controller

The remainder of this chapter describes the architecture in three sections centered around the processor module, the Uni-N memory controller and bridge IC, and the KeyLargo I/O controller IC.

# Microprocessor and Cache

The microprocessor is a PowerPC G4 with a built-in level 2 (L2) cache.

### PowerPC G4 Microprocessor

The PowerPC G4 microprocessor used in the eMac has many powerful features, including a pipelined system bus called MaxBus.

The PowerPC G4 has the following features:

- 32-bit PowerPC implementation

- superscalar PowerPC core

- Velocity Engine (AltiVec technology): 128-bit wide vector execution unit

- high bandwidth MaxBus

- dual 32 KB instruction and data caches (level 1)

- built-in 256 KB backside L2 cache

To find more information, see the reference at "PowerPC G4 Microprocessor" (page 43).

### Level 2 Cache

The data storage for the L2 cache consists of 256 KB of fast static RAM that is built into the microprocessor chip along with the cache controller. The built-in L2 cache runs at the same clock speed as the microprocessor.

# **Uni-N Bridge and Memory Controller**

The Uni-N custom IC is at the heart of the computer. It provides the bridging functionality between the processor, the memory system, the PCI-based I/O system, the AGP slot, and the FireWire and Ethernet interfaces.

### **Processor Bus**

The processor bus is a 133 MHz, 64-bit bus connecting the processor module to the Uni-N IC. In addition to the increased bus clock speed, the bus uses MaxBus protocols, supported by the Uni-N IC, for improved performance.

The MaxBus protocol includes enhancements that improve bus efficiency and throughput over the 60x bus. The enhancements include

- out of order completion

- address bus streaming

#### intervention

Out of order completion allows the memory controller to optimize the data bus efficiency by transferring whichever data is ready, rather than having to pass data across the bus in the order the transactions were posted on the bus. This means that a fast DRAM read can pass a slow PCI read, potentially enabling the processor to do more before it has to wait on the PCI data.

Address bus streaming allows a single master on the bus to issue multiple address transactions back-to-back. This means that a single master can post addresses at the rate of one every two clocks, rather thanone every three clocks, as it is in the 60x bus protocol.

Intervention is a cache-coherency optimization that improves performance for dual processor systems. If one processor modifies some data, that data first gets stored only in that processor's cache. If the other processor then wants that data, it needs to get the new modified values. In previous systems, the first processor must write the modified data to memory and then the second processor can read the correct values from memory. With intervention, the first processor sends the data directly to the second processor, reducing latency by a factor of ten or more.

## Main Memory Bus

The main memory bus is a 133 MHz, 64-bit bus connecting the main memory to the Uni-N IC. The memory interface is synchronized to the 60x bus interface at 133 MHz.

Main memory is provided by one or two PC-133 DIMMs (dual inline memory modules). For more information about memory DIMMs, see "RAM Expansion" (page 39).

# **Accelerated Graphics Port Bus**

The accelerated graphics port (AGP) bus is a 66 MHz, 32-bit bus connecting the AGP IC to the Uni-N IC. The AGP bus provides faster access to main memory than previous designs using the PCI bus.

The AGP bus is a superset of the PCI bus, with the addition of separate address lines so it does not multiplex address and data when running in AGP mode. Having a separate address bus allows the AGP bus to pipeline addresses, thereby improving performance.

To further improve the performance of the AGP bus, the Uni-N IC supports a graphics address remapping table (GART). Because the virtual memory system organizes main memory as randomly distributed 4 KB pages, DMA transactions for more than 4 KB of data must perform scatter-gather operations. To avoid this necessity for AGP transactions, the GART is used by the AGP bridge in the Uni-N to translate a linear address space for AGP transactions into physical addresses in main memory.

## Video Display Subsystem

The display subsystem consists of a graphics controller IC and 32 MB of DDR on the main logic board. The graphics controller IC is an Radeon 7500. It contains 2D and 3D acceleration engines, front-end and back-end scalers, a CRT controller, and an AGP bus interface with bus master capability.

The interface between the graphics IC and the rest of the system is an AGP (accelerated graphics port) bus on the Uni-N IC. To give the graphics IC fast access to system memory, the AGP bus has separate address and data lines and supports deeply pipelined read and write operations. The AGP bus has 32 data lines and a clock speed of 66 MHz.

The graphics IC uses a graphics address remapping table (GART) to translate AGP logical addresses into physical addresses. The graphics driver software can allocate memory in both the dedicated SDRAM and the main memory.

For information about the display and supported resolutions, see "Video Display" (page 31).

### **PCI** Bus

The 33 MHz, 32-bit PCI bus connects the Uni-N IC to the boot ROM and the KeyLargo I/O controller. Also, the AirPort Extreme module is connected via the PCI bus.

The Uni-N IC used in the eMac supports a PCI feature called write combining. This feature allows sequential write transactions involving the Memory Write or Memory Write and Invalidate commands to be combined into a single PCI transaction. The memory write transactions being combined must be to sequential, ascending, and non-overlapping PCI addresses. Placing an eieio or sync command between the write commands prevents any write combining.

### **Boot ROM**

The boot ROM consists of 1 MB of on-board flash EPROM. The boot ROM includes the hardware-specific code and tables needed to start up the computer, to load an operating system, and to provide common hardware access services.

### **Ethernet Controller**

The Uni-N IC includes an Ethernet media access controller (MAC). As a separate I/O channel on the Uni-N IC, it can operate at its full capacity without degrading the performance of other peripheral devices. The MAC also provides DMA support for the Ethernet interface.

The MAC implements the link layer. It is connected to a PHY interface IC that provides 10Base-T or 100Base-T operation over a standard twisted-pair interface. The operating speed of the link is automatically negotiated by the PHY and the bridge or router to which the Ethernet port is connected. For information about the port, see "Ethernet Port" (page 27).

### FireWire 400 Controller

The Uni-N IC includes an IEEE 1394a FireWire 400 controller that implements the FireWire link layer. The controller supports a maximum data rate of 400 Mbits (50 MBytes) per second.

The controller IC implements the FireWire link layer. A physical layer IC, called a PHY, implements the electrical signalling protocol of the FireWire interface. The PHY supports two FireWire 400 ports by way of external connectors in the I/O bay.

The PHY is powered as long as the computer is connected to AC power. While the PHY is operating, it acts as a repeater from one port to another so that the FireWire bus remains connected. For more information, see "FireWire 400 Ports" (page 24).

# KeyLargo I/O Controller

The KeyLargo custom IC is the third major component of the architecture. It provides all the I/O functions except Ethernet and FireWire. The KeyLargo IC provides two USB root hubs, an Ultra DMA/66 interface, and support for the communication slot and the sound IC.

## **DMA Support**

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the following I/O channels:

- Ultra DMA/66 interface

- communication slot interface

- IIS channel to the sound subsystem

The DB DMA system provides a scatter-gather process based on memory-resident data structures that describe the data transfers. The DMA engine is enhanced to allow bursting of data files for improved performance.

# Interrupt Support

The interrupt controller for the eMac is an MPIC cell in the KeyLargo IC. In addition to accepting all the KeyLargo internal interrupt sources, the MPIC controller accepts external interrupts from dedicated interrupt pins and serial interrupts from the Uni-N serial interrupt stream. The signals from the Uni-N IC are synchronized to the operation of the MPIC circuitry, so there is no additional interrupt latency on the Uni-N interrupts.

### **USB** Interface

The KeyLargo IC implements two independent USB root hubs. USB port A is connected to one controller and the other two USB ports are connected to the other. The use of two independent hubs allows both USB ports to support high data rate devices at the same time with no degradation of their performance. Thus, if a user connects a high-speed (12 Mbps) device to USB port A and another high-speed device to the port B, both devices can operate at their full data rates.

Internally, the second port of one controller is routed to the modem slot for an internal USB modem. The second port of the other controller is connected to the third external USB port.

The external USB connectors support USB devices with data transfer rates of 1.5 Mbps or 12 Mbps. For more information about the connectors, see "USB Ports" (page 23).

USB devices connected to the eMac are required to support USB-suspend mode as defined in the USB specification. Information about the operation of USB-suspend mode on Macintosh computers is included in the Mac OS USB DDK API Reference. To obtain that document, please see the references at "USB Interface" (page 46).

The USB ports on the eMac comply with the Universal Serial Bus Specification 1.1 Final Draft Revision. The USB controllers comply with the Open Host Controller Interface (OHCI) specification.

### Ultra DMA Data Transfer

In the eMac, the KeyLargo IC provides an Ultra DMA channel that is connected to the internal hard disk drive. The Ultra DMA/66 and ATA-5, is an improved version of the EIDE interface.

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the Ultra DMA interface.

The cable is wired to select the internal hard disk drive as device 0 in an ATA Device 0/1 configuration.

### **Enhanced IDE Interface**

In the eMac, the KeyLargo IC provides an EIDE (enhanced IDE) interface that supports the internal optical disk drive.

The EIDE interface uses multiword DMA. The optical drive is connected as device 0 (master) in an ATA Device 0/1 configuration.

For information about the optical drive configurations, see "Combo Drive DVD-ROM/CD-RW" (page 29), "SuperDrive DVD-R/CD-RW Drive" (page 30), or "CD-ROM Drive" (page 29).

## Modem Slot Support

The KeyLargo IC has a traditional Macintosh serial port that is connected to the modem slot. The KeyLargo IC also provides digital audio to the slot in the form of an IIS port that shares pins with the serial port.

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the modem slot interface.

The internal hardware modem is a separate USB module that contains the datapump IC and the interface to the telephone line (DAA). For more information about the modem, see "Internal Modem" (page 27).

### Wireless LAN Module

The interface between the AirPort Extreme wireless LAN module and the KeyLargo IC is via the PCI bus.

The wireless LAN module contains a media access controller (MAC), a digital signal processor (DSP), and a radio-frequency (RF) section. The module has a connector for the cable to the antennas, which are built into the computer's enclosure.

The AirPort Extreme wireless LAN module is based on the IEEE specification of the 802.11g standard. The card transmits and receives data at up to 54 Mbps and is also compatible with 802.11b-standard systems, including AirPort. For information about its operation, see "AirPort Extreme Card" (page 28).

## Sound Circuitry

The sound circuitry is connected to the KeyLargo IC by standard IIC and IIS buses. The IIC bus provides configuration access to the audio circuitry ICs and the IIS bus is used for data transfers. The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the IIS port.

The audio circuitry performs digital audio processing and codec functions. The audio processing functions include output equalization and volume control. The codec functions include A-to-D and D-to-A conversion.

Stereo signals from the audio line-in jack drive the audio circuitry's A-to-D converter. Audio data from the KeyLargo IC drives the audio circuitry's D-to-A converter. Analog output from the D-to-A converter is routed to the headphone jack and the audio power amplifier.

The power amplifier drives the internal speaker. When headphones are connected to the headphone jack, the internal speaker is muted.

For a description of the features of the sound system, see "Sound System" (page 35).

### **Power Controller**

The power management controller in the eMac is a custom IC called the PMU99. It supports several power-saving modes of operation, including idle, doze, and sleep.

# **Devices and Ports**

This chapter describes both the built-in I/O devices and the ports for connecting external I/O devices. Each of the following sections describes an I/O port or device.

## **USB Ports**

The eMac has three Universal Serial Bus (USB) ports. The USB ports are connected to two separate USB root hubs, allowing two of the USB ports to support 12 Mbps devices at the same time with no degradation of their performance. See "Uni-N Bridge and Memory Controller" (page 17).

Note: The keyboard also contains a USB hub and two more USB ports. See "Keyboard and USB" (page 34).

For more information about USB on Macintosh computers, please refer to Apple Computer's *Mac OS USB DDK API Reference* and the other sources listed in "USB Interface" (page 46).

### **USB Connectors**

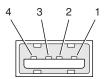

The USB ports use USB Type A connectors, which have four pins each. Two of the pins are used for power and two for data. Figure 3-1 (page 23) is an illustration of a Type A port; Table 3-1 (page 23) shows the signals and pin assignments.

Figure 3-1 USB Type A port and pins

**Table 3-1** Signals on the USB port

| Pin | Signal name | Description |

|-----|-------------|-------------|

| 1   | VCC         | +5 VDC      |

| 2   | D-          | Data –      |

| 3   | D+          | Data +      |

| 4   | GND         | Ground      |

**Devices and Ports**

The eMac provides 5 volt power to the USB ports. The maximum current available is 500 mA on each port.

The USB ports support both low-speed and high-speed data transfers, at up to 1.5 Mbits per second and 12 Mbits per second, respectively. High-speed operation requires the use of shielded cables.

The Macintosh system software supports all four data transfer types defined in the USB specification.

### **USB** Features

Features of the USB ports include power saving modes and the ability to boot the CD/ROM and Combo drive configurations of the eMac into Mac OS 9 using a USB mass-storage device.

### Wake Up From Sleep

USB devices can provide a remote wakeup function for the computer. The USB root hub in the computer is set to support remote wakeup whenever a device is attached to or disconnected from the bus. The keyboard that comes with the computer uses this method to wake the computer on a key press.

#### Connect and Resume

The KeyLargo IC contains special circuitry that allows the computer to wake from Sleep mode on connect, disconnect, and resume events. Compatible USB devices should support the USB-suspend mode defined in the USB specification.

### **USB Device Drivers**

Class drivers are software components that are able to communicate with many USB devices of a particular kind. If the appropriate class driver is present, any number of compliant devices can be plugged in and start working immediately without the need to install additional software.

### **USB Controller**

The eMac uses an Open Host Controller Interface (OHCI) controller for USB communication. Some early USB devices (most notably keyboards) can't interoperate with an OHCI controller. Those devices are not supported by the Macintosh USB system software.

## FireWire 400 Ports

The eMac has two external FireWire 400 IEEE 1394a ports. The features of the FireWire 400 ports are:

- Support serial I/O at 100, 200, and 400 Mbps (megabits per second)

- Share up to 8 watts of power when the computer system is on

- Support up to 62 devices

The FireWire 400 hardware and software provided with the eMac are capable of all asynchronous and isochronous transfers defined by the IEEE 1394a standard.

## FireWire 400 Device Programming

A generic driver for mass storage devices is included in the system software. This driver is used only when a vendor-specific driver cannot be found. Apple recommends that users install vendor-provided drivers for maximum performance and functionality.

A driver for DV (digital video) is included in QuickTime 4.0 and later versions.

The eMac can boot from a FireWire 400 storage device that implements SBP-2 (Serial Bus Protocol) with the RBC (reduced block commands) command set. Detailed information is available only under non-disclosure agreement; contact Developer Technical Support at dts@apple.com.

When connected to another computer by a FireWire 400 bus, the eMac can operate as a mass storage device. See "Target Disk Mode" (page 26).

For additional information about the FireWire 400 interface and the Apple APIs for FireWire 400 device control, refer to the resources listed in "FireWire Interface" (page 46).

### FireWire 400 Connector

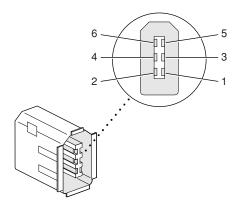

The FireWire 400 connector has six contacts, as shown in Figure 3-2 (page 25). The connector signals and pin assignments are shown in Table 3-2 (page 25).

Figure 3-2 FireWire 400 connector

**Table 3-2** Signals on the FireWire 400 connector

| Pin | Signal name | Description                                    |  |

|-----|-------------|------------------------------------------------|--|

| 1   | Power       | unregulated DC; 17-24 V no load                |  |

| 2   | Ground      | Ground return for power and inner cable shield |  |

| 3   | TPB-        | Twisted-pair B, differential signals           |  |

| 4   | TPB+        | Twisted-pair B, differential signals           |  |

| 5   | TPA-        | Twisted-pair A, differential signals           |  |

| Pin   | Signal name | Description                          |  |  |

|-------|-------------|--------------------------------------|--|--|

| 6     | TPA+        | Twisted-pair A, differential signals |  |  |

| Shell | _           | Outer cable shield                   |  |  |

When the computer is on, the power pin provides a maximum voltage of 24 V (no load) and up to 8 W total power (shared by both connectors). Zero voltage is present at the power pin when the computer is in sleep mode or when it is off.

The FireWire 400 PHY is powered as long as the computer is connected to AC power. While the PHY is operating, it acts as a repeater from one port to another so that the FireWire 400 bus remains connected.

Pin 2 of the 6-pin FireWire 400 connector is ground for both power and inner cable shield. If a 4-pin connector is used on the other end of the FireWire 400 cable, its shell should be connected to the wire from pin 2.

The signal pairs are crossed in the cable itself so that pins 5 and 6 at one end of the cable connect with pins 3 and 4 at the other end. When transmitting, pins 3 and 4 carry data and pins 5 and 6 carry clock; when receiving, the reverse is true.

For additional information about the FireWire 400 interface and the Apple APIs for FireWire 400 device control, developers should refer to the resources listed in "FireWire Interface" (page 46).

## Target Disk Mode

The user has the option at boot time to put the computer into a mode of operation called Target Disk Mode (TDM).

When the eMac is in Target Disk Mode and connected to another Macintosh computer by a FireWire cable, the eMac operates like a FireWire mass storage device with the SBP-2 (Serial Bus Protocol) standard. Target Disk Mode has two primary uses:

- high-speed data transfer between computers

- diagnosis and repair of a corrupted internal hard drive

The eMac can operate in Target Disk Mode as long as the other computer has a FireWire port and either Mac OS X (any version) or Mac OS 9 with FireWire software version 2.3.3 or later.

To put the eMac into Target Disk Mode, restart the eMac and hold down the T key until the FireWire icon appears on the display. Then connect a FireWire cable from the eMac to the other computer. When the other computer completes the FireWire connection, a hard disk icon appears on its desktop.

If the FireWire cable is disconnect or the eMac turned off while in Target Disk Mode, an alert appears on the other computer.

To take the eMac out of Target Disk Mode, drag the hard-disk icon on the other computer to the trash, then press the power button on the eMac.

### **Ethernet Port**

The eMac has a built-in 10/100 Mbps Ethernet port. The user can connect it to an Ethernet cable from a hub, switch, or router, or to another Macintosh computer using a cross-connect cable. The connected device can be either a 10Base-T or a 100Base-TX device; the port automatically detects which type of device is connected.

The connector for the Ethernet port is a an RJ-45 connector located on the I/O panel. Table 3-3 (page 27) shows the signals and pin assignments on the connector.

**Table 3-3** Signals on the Ethernet connector

| Pin | Signal name | Signal definition        |

|-----|-------------|--------------------------|

| 1   | ТХР         | Transmit (positive lead) |

| 2   | TXN         | Transmit (negative lead) |

| 3   | RXP         | Receive (positive lead)  |

| 4   | _           | Not used                 |

| 5   | _           | Not used                 |

| 6   | RXN         | Receive (negative lead)  |

| 7   | _           | Not used                 |

| 8   | _           | Not used                 |

The Ethernet interface in the eMac conforms to the ISO/IEC 802.3 specification, where applicable.

## Internal Modem

Except for the educational configuration, the eMac has an internal, USB fax modem. The telephone connector for the modem is an RJ-11 connector on the I/O panel. A telephone cable is included with the computer.

The Micro Dash modem has the following features:

- modem bit rates up to 56 Kbps (supports V.92 and K56flex modem standards)

- Group 3 fax modem bit rates up to 14.4 Kbps

The modem appears to the system as a serial port that responds to the typical AT commands. The modem provides an analog sound output for monitoring the progress of the modem connection.

### AirPort Extreme Card

The eMac supports the AirPort Extreme Card, an internal wireless LAN module connected to the PCI bus. The AirPort Extreme Card is available as a build-to-order option or as a user-installable upgrade.

By communicating wirelessly with a base station, the AirPort Extreme Card can be used for Internet access, email access, and file exchange. A base station provides the connection to the Internet or the bridge between the wireless signals and a wired LAN or both. The AirPort Extreme Base Station has connectors for a wired LAN or WAN, a DSL or cable modem, and a standard telephone line using the built-in 56 Kbps modem that is available on some base station configurations.

AirPort Extreme transmits and receives data at speeds up to 54 Mbps, comparable to wired networking speeds. AirPort Extreme is compatible with earlier AirPort systems as well as other devices that adhere to the IEEE 802.11b and 802.11g standards. For more information about Wi-Fi and compatibility, see the reference at "Wireless Networks" (page 46).

**Note:** As is the case with the existing IEEE 802.11b standard, actual data throughput speeds will be lower than the indicated maximum connection speeds. Inherent in wireless LAN systems, bandwidth overhead is required for wireless routing, scrambling, security error correction, and other processes.

## **Data Security**

AirPort Extreme has several features designed to maintain the security of the user's data:

- The system uses direct-sequence spread-spectrum (DSSS) technology that uses a multibit spreading code that effectively scrambles the data for any receiver that lacks the corresponding code.

- The system can use an Access Control List of authentic network client ID values (wireless and MAC Addresses) to verify each client's identity before granting access to the network.

- AirPort Extreme supports over-the-air encryption standards, including 40-bit and 128-bit WEP and WPA.

- The AirPort Extreme Base Station can be configured to use NAT (Network Address Translation), protecting data from would-be Internet hackers.

- The AirPort Extreme Base Station can authenticate users by their unique Ethernet IDs, preventing unauthorized computers from logging into a network. Network administrators can take advantage of RADIUS compatibility, used for authenticating users over a remote server. Smaller networks can offer the same security using a local look-up table located within the base station.

As an additional data security measure, VPN can be used in conjunction with the AirPort Extreme data security.

### AirPort Extreme Hardware

The AirPort Extreme Card is a wireless LAN module based on the IEEE specification of the 802.11g standard using both OFDM (orthogonal frequency-division multiplexing) and DSSS technologies. Using DSSS, AirPort Extreme is interoperable with PC-compatible wireless LANs that conform to the 802.11b standard at speeds of 11 Mbps, 5.5 Mbps, 2 Mbps, and 1 Mbps. Using OFDM, AirPort Extreme is compatible with all 802.11g standard speeds.

**Devices and Ports**

Two AirPort Extreme antennas are built into the computer's enclosure. One antenna is always used for transmitting. Either of the two antennas may be used for receiving. Using a diversity technique, the AirPort Extreme Card selects the antenna that gives the best reception.

### AirPort Extreme Software

Software that is provided with the AirPort Extreme Card includes

- AirPort Setup Assistant, an easy-to-use program that guides the user through the steps necessary to set up the AirPort Extreme Card or set up an AirPort Extreme Base Station.

- Users can switch between wireless networks and can create and join peer-to-peer networks. These functions are accessed via the AirPort Menu-Extra pulldown in System Preferences.

- AirPort Admin Utility, a utility for advanced users and system administrators. With it the user can edit the administrative and advanced settings needed for some advanced configurations.

### Hard Disk Drive

The internal hard disk drive has a storage capacity of 40 GB for the CD-ROM and Combo drive configurations and 80 GB for the SuperDrive configuration. Some configurations have 80 GB and 160 GB build-to-order options. The drive uses the ATA interface and is configured as Device 0 via Cable Select setting. The drive is capable of Ultra DMA Mode 4, 66 megabytes per second of data transfer speed. This interface is compatible with ANSI-NCITS industry standard ATA/ATAPI-6.

The software that supports the internal hard disk is similar to that in previous Macintosh models with internal IDE drives and includes DMA support. To obtain information about that software and about the ANSI standard for the Ultra DMA data transfer, see "ATA Interface" (page 45).

# **CD-ROM Drive**

One configuration of the eMac has an internal CD-ROM drive. The drive has a tray for loading the disc. The drive is capable of reading at 32x speed.

Digital audio signals from the CD-ROM drive can be played through the sound outputs under the control of System Preferences.

The CD-ROM drive is an ATAPI drive and is cable-select jumpered as master in an ATA Device configuration.

## Combo Drive DVD-ROM/CD-RW

One configuration of the eMac has a tray-loading combination DVD-ROM and CD-RW drive. The Combo drive can read DVD media and read and write CD media, as shown in Table 3-4 (page 30). The DVD-ROM/CD-RW drive also provides DVD-Video playback.

Table 3-4 Types of media read and written by the Combo drive

| Media type | Reading speed | Writing speed |

|------------|---------------|---------------|

| DVD-ROM    | 8x (CAV)      | _             |

| DVD-R      | 4x max (CAV)  | _             |

| CD-R       | 32x (CAV)     | 32x max       |

| CD-RW      | 20x (CAV)     | 10x (CLV)     |

| CD-ROM     | 32x (CAV)     | -             |

Digital audio signals from the DVD-ROM/CD-RW drive can be played through the sound outputs under the control of System Preferences.

The Combo drive is connected as device 0 (master) to an independent ATA interface capable of multi-word DMA mode 2, 16 megabytes per second. This interface is compatible with ANSI-NCITS industry standard ATA/ATAPI-5.

# SuperDrive DVD-R/CD-RW Drive

One configuration of the eMac has a tray-loading CD-RW and DVD-R SuperDrive. The drive can read and write DVD media and CD media, as shown in Table 3-5 (page 30). The SuperDrive also provides DVD-Video playback with DVD MPEG 2 decode.

**Table 3-5** Types of media read and written by the SuperDrive

| Media type   | Reading speed                      | Writing speed                 |

|--------------|------------------------------------|-------------------------------|

| DVD-R        | 2x                                 | 4x, 2x, 1x depending on media |

| DVD-ROM      | 8x (single layer), 2x (dual layer) | _                             |

| DVD-RW       | 2x                                 | 2x, 1x depending on media     |

| CD-R         | 32x max                            | 16x                           |

| CD-RW        | 32x max                            | 8x, 4x depending on media     |

| CD or CD-ROM | 32x max                            | -                             |

Digital audio signals from the SuperDrive can be played through the sound outputs under the control of System Preferences.

The SuperDrive is connected as device 0 (master) to an independent ATA interface capable of multi-word DMA mode 2, 16 megabytes per second. This interface is compatible with ANSI-NCITS industry standard ATA/ATAPI-5.

# Video Display

The built-in video display uses a 17-inch CRT (16-inch viewable diagonal). The CRT uses shadow-mask technology and has a dot pitch of 0.25 mm. The display has a fixed horizontal scan rate (72 kHz) and supports five resolutions. Table 3-6 (page 31) lists the resolutions and the vertical scan rates supported.

The display supports pixel depths up to 24 bits (millions of colors) at all resolutions.

**Table 3-6** Display resolutions and pixel depths

| Resolution  | Vertical rate | Pixel depth |

|-------------|---------------|-------------|

| 640 by 480  | 138 Hz        | 24 bits     |

| 800 by 600  | 112 Hz        | 24 bits     |

| 1024 by 768 | 89.0 Hz       | 24 bits     |

| 1152 by 864 | 80.0 Hz       | 24 bits     |

| 1280 by 960 | 72.0 Hz       | 24 bits     |

# **External Display Port**

The eMac has a video output port for connecting an external video monitor or projector. The port supports both RGB and composite/S-video signals (for VGA and TV) by means of adapters. The port detects the type of adapter connected to it and programs the graphics IC to provide the appropriate type of video signals, as shown in the table below.

Table 3-7 Display adapters

| Adapter type        | Video signals                    | Connector type(s)           |

|---------------------|----------------------------------|-----------------------------|

| Apple VGA adapter   | RGB                              | VGA 15-pin miniature D-type |

| Apple Video adapter | Composite and S-video TV signals | RCA and S-video             |

Resolutions supported are nominally 640 by 480, 800 by 600, and 1024 by 768 pixels (based on the EDID and attached monitor). When either type of display adapter is connected, the settings for the resolutions with multiple vertical refresh rates are selectable in System Preferences.

Composite video and S-video signals can be displayed on either an NTSC display or a PAL display. When a display is connected by way of the video adapter, the computer detects the type of adapter and enables the composite and S-video outputs. The settings for the resolutions and standards (NTSC or PAL) are then selectable in the monitor control panel or control strip.

The video output mirrors the flat panel display: internal and external video share the same buffer, and the hardware sends the image to both displays.

Note: A VGA display adapter is required to convert to VGA display.

# Video Display Connector

The video display connector is a 14-pin rectangular connector (Hosiden TCX3143 or compatible). The connector pins are identified in Figure 3-3 (page 32).

Figure 3-3 Video display connector

The eMac detects the type of display adapter that is plugged in and programs the graphics IC to route the appropriate video signals to the connector. The signal assignments on the video connector are shown in Table 3-8 (page 32). The signal assignments for the video adapter are shown in Table 3-9 (page 32).

**Table 3-8** Video signals for a VGA display

| Pin | Signal name  | Pin | Signal name   |

|-----|--------------|-----|---------------|

| 1   | Ground       | 8   | +5 volts      |

| 2   | VSync        | 9   | Blue video    |

| 3   | Hsync        | 10  | DDC data      |

| 4   | Red return   | 11  | DDC clock     |

| 5   | Red video    | 12  | Ground        |

| 6   | Green return | 13  | /Cable detect |

| 7   | Green video  | 14  | Blue return   |

**Table 3-9** Video signals for a TV display

| Pin | Signal name | Pin | Signal name     |

|-----|-------------|-----|-----------------|

| 1   | Ground      | 8   | +5 volts        |

| 2   | n.c.        | 9   | Composite video |

| 3   | n.c.        | 10  | DDC data        |

| Pin | Signal name | Pin | Signal name                |

|-----|-------------|-----|----------------------------|

| 4   | Ground      | 11  | DDC clock                  |

| 5   | S-video C   | 12  | Ground                     |

| 6   | Ground      | 13  | Ground (for /Cable Detect) |

| 7   | S-video Y   | 14  | Ground                     |

The cable detect function on pin 13 is implemented by connecting pin 13 to ground in the display cable. The computer detects the video adapter by reading its EDID (Extended Display Identification Data) via DDC.

The video display connector is compliant with the VESA specification (DDC version 3).

## Older Monitors Not Supported

The computer supports current video monitors. The detection scheme on some older monitors are not supported and will use default configurations, including the following Apple monitors:

- Multiple Scan 17

- Multiple Scan 20

- AudioVision 14

- Apple Hi-Res RGB

- Apple 16" Color

- Apple Hi-Res Monochrome

- Macintosh 12" RGB

# Keyboard

The eMac comes with an Apple Keyboard. It is a USB compatible full-size keyboard with 16 function keys and separate groups of numeric keypad and editing keys.

The keyboard also provides two additional USB ports; see "Keyboard and USB" (page 34).

# **Keyboard Features**

Here is a list of the features of the Apple Keyboard.

- Fixed slope keyboard

- 109 keys (on the ANSI versions)

- 16 function keys

- 6 editing keys (Page Up, Page Down, Home, End, Forward Delete, and Help)

- USB HID Consumer Page Usage multimedia control keys

- Full travel, standard pitch keys on alphanumeric, editing, and keypad sections, including function keys and cursor position keys

- Localized worldwide: 33 versions, 3 standard layouts (ANSI, JIS, ISO)

- LED indicator on the Num Lock key

- USB hub functionality with two Type A USB bus-powered ports

**Note:** There is no power key on this keyboard.

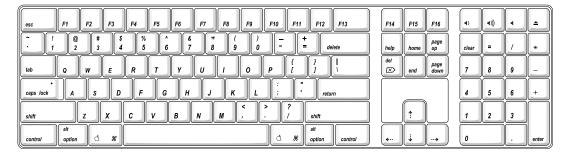

## **Keyboard Layout**

There are localized versions of the Apple Keyboard for use in different parts of the world. The three standards used are ANSI (US and North America), JIS (Japan), and ISO (Europe). Figure 3-4 (page 34) shows the keyboard layout for the ANSI keyboard.

Applications can determine which keyboard is connected by calling the Gestalt Manager and checking for the corresponding value of the <code>gestaltKeyboardType</code> selector.

Figure 3-4 ANSI keyboard layout

# MultiMedia Control Keys

The keyboard has six multimedia keys: Volume Up, Volume Down, Mute, Brightness Up (F15), Brightness Down (F14), and Eject. Theses keys provide direct control of the features on the computer by way of the USB.

## Keyboard and USB

The Apple Keyboard is designed to work with the eMac by way of the USB ports. The keyboard has a captive cable with a USB Type A connector. The keyboard is a bus-powered USB hub with two USB Type A ports.

**Warning:** A bus-powered hub does not provide enough power to support a second bus-powered hub. To use a second bus-powered hub with an eMac, connect it to the second USB port on the computer, not to a port on the Apple USB keyboard.

**Devices and Ports**

Apple provides a HID class driver for the Apple USB keyboard, which supports the USB boot protocol. Other keyboards intended for use on the Macintosh platform must support the HID boot protocol, as defined in the USB Device Class Definition for Human Interface Devices (HIDs). For information about the USB HID definition, see the HID reference in "USB Interface" (page 46).

### Mouse

The eMac comes with an Apple Mouse. The mouse case is made of polycarbonate plastic like the computer.

The Apple Mouse uses optical tracking in place of the traditional rolling ball. It works on almost any surface, though non-reflective, opaque surface without repetitive patterns work best.

# Sound System

The sound system provides high-quality stereo sound input and output through the built-in microphone and speakers. The user can also connect external input and output devices by way of the sound input and output jacks.

**Note:** The eMac also supports speakers and microphones that connect to the USB port.

To maintain the highest fidelity when digital audio program material from CDs is played, the audio data is kept in digital form until just before being sent to the internal speakers or the headphone jack.

The sound system is based on a set of ICs that perform digital audio processing functions such as output equalization, dynamic range compression, and volume control.

The sound system supports sample sizes up to 16 bits at a sample rate of 44.1 kHz.

## Sound Inputs

The sound system accepts inputs from five possible sources:

- built-in microphone

- external audio line-in jack

- sound from internal optical drive

- call progress audio from the internal modem

- sound from USB audio devices

- sound input from FireWire audio devices

### **Built-in Microphone**

The sound signal from the built-in microphone is amplified by a preamp and sent to the codec circuits in the audio IC.

### External Audio Line-in Jack

The audio line-in jack is a 3.5 mm miniature phone jack located on the I/O panel on the right side of the computer. The line-in jack accepts line-level stereo signals. It also accepts a stereo miniplug-to-RCA cable adapter for connecting stereo equipment to the computer.

The line-in jack signal connections are:

- tip: audio left channel

- ring: audio right channel

- sleeve: audio ground

The line-in jack has the following electrical characteristics:

- input impedance: nominal 40 kilohms

- maximum level: nominal 2 V rms (5.6 V peak-to-peak)

## **Sound Outputs**

The sound system sends computer-generated sounds to two destinations:

- built-in stereo speakers

- headphone jack

### **Internal Speakers**

The computer has two internal speakers. The computer turns off the sound signals to the internal speakers under the following conditions:

- when headphones are plugged into the headphone jack

- when external USB speakers are connected and selected in Sound Preferences Output pane

- during sleep mode

### Headphone Jack

The headphone jack is located on the I/O panel on the right side of the computer. The jack provides enough current to drive a pair of low-impedance headphones.

The headphone jack has the following electrical characteristics:

output impedance: 5.0 ohms (nominal)

**Devices and Ports**

■ maximum level: 1.5 Vrms (4.2 V peak-to-peak)

Headphones should have an impedance not lower than the recommended minimum impedance of 32 ohms. Headphones with lower impedance can be used, but with some degradation in performance.

# **Sound Specifications**

The frequency response of the sound circuits, not including the microphone and speakers, is within plus 1 dB or minus 3 dB from 20 Hz to 20 kHz.

Total harmonic distortion plus noise (THD+N) as a percentage of full scale are shown in Table 3-10 (page 37).

Table 3-10

Distortion specifications

| Connector                         | THD+N |

|-----------------------------------|-------|

| Line input                        | 0.03% |

| Headphone jack, open circuit      | 0.03% |

| Headphone jack, 32 ohm headphones | 0.5%  |

The signal-to-noise ratios (SNR) for various inputs and outputs are shown in Table 3-11 (page 37). The values shown are unweighted.

Table 3-11 SNR specifications

| Connector          | Signal-to-noise ratio |

|--------------------|-----------------------|

| Microphone         | 65 dB                 |

| Headphone jack     | 90 dB                 |

| Line input         | 85 dB                 |

| Internal CD or DVD | 90 dB                 |

#### **CHAPTER 3**

**Devices and Ports**

# RAM Expansion

This chapter tells how to gain access to the expansion slots in the eMac and describes the RAM expansion modules.

## **RAM Expansion Slots**

The eMac has two RAM expansion slots. The slots accept standard PC-133, 168-pin DIMMs (dual inline memory modules) that use SDRAM devices. A DIMM for a eMac can contain either 64, 128, 256, or 512 MB of memory.

A door on the bottom of the computer provides access to the RAM expansion slots. Before opening the bottom door, the user should place the computer face down on a soft cloth.

When the door is open, the portion of the main logic board that contains the two RAM expansion slots is visible. The top slot is normally occupied by the factory-installed RAM DIMM. Either RAM expansion slot can accept a user-installed DIMM.

**Important:** The user should be reminded to observe the usual precautions to avoid damage to the electronic components due to static electricity.

## **RAM Expansion Modules**

The RAM expansion modules for the eMac are 168-pin SDRAM DIMMs that are 3.3 volt, unbuffered, 8-byte, non-parity, and PC-133 compliant. The speed of the SDRAM devices must be rated at 140 MHz (7 ns) or faster.

**Important:** RAM expansion DIMMs for the eMac must use SDRAM devices. If the user installs a DIMM that uses EDO or SGRAM devices, the computer will beep several times when the user attempts to restart the computer.

# Mechanical Design of RAM DIMMs

The mechanical characteristics of the RAM expansion DIMM are given in the JEDEC specification for the 168-pin 8-byte DRAM DIMM. The specification number is JEDEC MO-161-D. To obtain a copy, see the reference information at "RAM Expansion Modules" (page 45).

The maximum height of DIMMs for use in the eMac is 1.50 inches.

#### **Electrical Design of RAM DIMMs**

The electrical characteristics of the RAM DIMM are given in section 4.5.6 of the JEDEC Standard 21-C. The specification is available from the Electronics Industry Association's website. The specification defines several attributes of the DIMM, including storage capacity and configuration, connector pin assignments, and electrical loading. To obtain a copy, see the reference information at "RAM Expansion Modules" (page 45).

The presence detect serial EEPROM specified in the JEDEC standard is required and must be set to properly define the DIMM configuration. Details about the required values to be stored in the presence detect EEPROM can be found in sections 4.5.4 and 4.1.2.5 of the JEDEC standard 21-C specification.

The RAM DIMMs are required to be PC-133 compliant. To obtain information about the PC-133 specification, see the reference information at "RAM Expansion Modules" (page 45).

The SDRAM devices used in the RAM expansion modules must be self-refresh type devices for operation from a 3.3-V power supply. The speed of the SDRAM devices must be 140 MHz or greater, corresponding to a cycle time of 7 ns or less, as required by the PC-133 specification.

#### **DIMM Configurations**

The largest DIMM supported is a two-bank DIMM of 512 MB using 256 Mbit SDRAM devices. The largest bank size supported by the memory controller is 256 MB. The maximum number of devices per DIMM is 16.

Table 4-1 (page 40) shows information about the different sizes of SDRAM devices used in the memory modules. The memory controller supports SDRAM devices of 64, 128, 256 Mbit sizes. The device configurations include three specifications: address range, word size, and number of banks. For example, a 1 M by 16 by 4 device addresses 1 M, stores 16 bits at a time, and has 4 banks.

The third column in Table 4-1 (page 40) specifies the number of devices needed to make up the 8-byte width of the data bus. The fourth column in the table shows the size of each bank of devices, which is based on the number of internal banks in each device and the number of devices per bank. The last column shows the memory size of the largest DIMM with that device size that the computer can accommodate.

**Table 4-1** Sizes of RAM expansion devices and DIMMs

| SDRAM device size | Device configuration | Devices per bank | Size of each bank | Size of DIMM |

|-------------------|----------------------|------------------|-------------------|--------------|

| 64 Mbits          | 4 M x 8 x 2          | 8                | 64 MB             | 128 MB       |

| 64 Mbits          | 2 M x 8 x 4          | 8                | 64 MB             | 128 MB       |

| 64 Mbits          | 2 M x 16 x 2         | 4                | 32 MB             | 128 MB       |

| 64 Mbits          | 1 M x 16 x 4         | 4                | 32 MB             | 128 MB       |

| 64 Mbits          | 1 M x 32 x 2         | 2                | 16 MB             | 128 MB       |

| 64 Mbits          | 512 K x 32 x 4       | 2                | 16 MB             | 128 MB       |

| 128 Mbits         | 8 M x 8 x 2          | 8                | 128 MB            | 256 MB       |

| 128 Mbits         | 4 M x 8 x 4          | 8                | 128 MB            | 256 MB       |

| 128 Mbits         | 4 M x 16 x 2         | 4                | 64 MB             | 256 MB       |

| SDRAM device size | Device configuration | Devices per bank | Size of each bank | Size of DIMM |

|-------------------|----------------------|------------------|-------------------|--------------|

| 128 Mbits         | 2 M x 16 x 4         | 4                | 64 MB             | 256 MB       |

| 128 Mbits         | 2 M x 32 x 2         | 2                | 32 MB             | 256 MB       |

| 128 Mbits         | 1 M x 32 x 4         | 2                | 32 MB             | 256 MB       |

| 256 Mbits         | 8 M x 8 x 4          | 8                | 256 MB            | 512 MB       |

| 256 Mbits         | 4 M x 16 x 4         | 4                | 128 MB            | 256 MB       |

| 256 Mbits         | 2 M x 32 x 4         | 2                | 64 MB             | 128 MB       |

The eMac accepts either one or two DIMMs. Any of the supported DIMM sizes can be installed in either slot. The memory controller configures the combined memory of the DIMMs into a contiguous array of memory addresses.

**Note:** The eMac does not use memory interleaving, so installing two DIMMs of the same size does not result in any performance gain.

#### **RAM Addressing**

Signals A[0] – A[12] and BA[0] – BA[1] on each RAM DIMM make up a 15-bit multiplexed address bus that can support several different types of SDRAM devices. Table 4-2 (page 41) lists the types of devices that can be used in the eMac by size, configuration, and sizes of row and column addresses.

**Important:** The eMac supports only the types of SDRAM devices listed in Table 4-2 (page 41). Other types of DRAM devices should not be used with this computer.

**Table 4-2** Address multiplexing modes for SDRAM devices

| Device size | Device configuration | Size of row address | Size of column address |

|-------------|----------------------|---------------------|------------------------|

| 64 Mbits    | 4 M x 8 x 2          | 13                  | 9                      |

| 64 Mbits    | 2 M x 8 x 4          | 12                  | 9                      |

| 64 Mbits    | 2 M x 16 x 2         | 13                  | 8                      |

| 64 Mbits    | 2 M x 16 x 2         | 11                  | 10                     |

| 64 Mbits    | 1 M x 16 x 4         | 12                  | 8                      |

| 64 Mbits    | 1 M x 32 x 2         | 11                  | 9                      |

| 64 Mbits    | 512 K x 32 x 4       | 11                  | 8                      |

| 128 Mbits   | 8 M x 8 x 2          | 13                  | 10                     |

| 128 Mbits   | 4 M x 8 x 4          | 12                  | 10                     |

#### **CHAPTER 4**

#### **RAM Expansion**

| Device size | Device configuration | Size of row address | Size of column address |

|-------------|----------------------|---------------------|------------------------|

| 128 Mbits   | 4 M x 16 x 2         | 13                  | 9                      |

| 128 Mbits   | 2 M x 16 x 4         | 12                  | 9                      |

| 128 Mbits   | 2 M x 32 x 2         | 13                  | 8                      |

| 128 Mbits   | 1 M x 32 x 4         | 12                  | 8                      |

| 256 Mbits   | 8 M x 8 x 4          | 13                  | 10                     |

| 256 Mbits   | 4 M x 16 x 4         | 13                  | 9                      |

| 256 Mbits   | 2 M x 32 x 4         | 13                  | 8                      |

# Supplemental Reference Documents

For more information about the technologies mentioned in this developer note, consult the following references.

For information about older models of Macintosh computers, refer to the developer notes archive at

http://developer.apple.com/documentation/Hardware/hardware2.html

## **Apple Technical Notes**

Apple Technical Notes answer many specific questions about the operation of Macintosh computers and the Mac OS. The Technical Notes are available on the Technical Note website at

http://developer.apple.com/technotes/

## 3D Graphics

Developers of 3D graphics for games should know about OpenGL for Macintosh¨, a version of SGI's application programming interface (API) and software library for 3D graphics.

Information is available on the World Wide Web at

http://www.apple.com/opengl

Developer support and documentation is available at

http://developer.apple.com/opengl/

# PowerPC G4 Microprocessor

Information about the PowerPC G4 microprocessor is available on the World Wide Web at

http://e-www.motorola.com/webapp/sps/site/prod\_summary.jsp?code=MPC7457&nodeld=018rH3bTdG8653

### Velocity Engine (AltiVec)

Velocity Engine is Apple's name for the AltiVec vector processor in the PowerPC G4 microprocessor. Apple provides support for developers who are starting to use the Velocity Engine in their applications. Documentation, development tools, and sample code are available on the World Wide Web, at

http://developer.apple.com/hardwaredrivers/ve/index.html

AltiVec Technology Programming Environments Manual (AltiVec PEM) is a reference guide for programmers. It contains a description for each instruction and information to help in understanding how the instruction works. Obtain a copy of the AltiVec PEM through the Motorola AltiVec site on the World Wide Web, at

http://www.freescale.com/webapp/sps/site/overview.jsp?nodeId=02VS0I81285Nf2

#### Mac OS X

For information about Mac OS X, see Apple's developer website at

http://developer.apple.com/documentation/MacOSX/MacOSX.html

O'Reilly & Associates publishes a series of books about Mac OS X development. The books in this series have been technically reviewed by Apple engineers and are recommended by the Apple Developer Connection.

#### I/O Kit

The I/O Kit is part of Darwin, the operating system foundation for Mac OS X. The documentation for I/O Kit is available on Apple's Darwin website at

http://developer.apple.com/documentation/Darwin/Darwin.html/

# **Open Firmware**

The software firmware implemented on current Macintosh computers follows the standard defined by the Open Firmware IEEE 1274-1994 specification. Three Technical Notes provide an introduction to Open Firmware on the Macintosh platform. They are:

TN1061: Open Firmware, Part I, available at

http://developer.apple.com/technotes/tn/tn1061.html

TN1062: Open Firmware, Part II, available at

http://developer.apple.com/technotes/tn/tn1062.html

TN1044: Open Firmware, Part III, available at

#### **APPENDIX A**

Supplemental Reference Documents

#### http://developer.apple.com/technotes/tn/tn1044.html

Other Technical Notes provide additional information about Open Firmware on the Macintosh.

TN2000: PCI Expansion ROMs and You, at

http://developer.apple.com/technotes/tn/tn2000.html

TN2001: Running Files from a Hard Drive in Open Firmware, at

http://developer.apple.com/technotes/tn/tn2001.html

TN2004: Debugging Open Firmware Using Telnet, available at

http://developer.apple.com/technotes/tn/tn2004.html

### **RAM Expansion Modules**

The eMac uses 168-pin SDRAM DIMMs. The mechanical characteristics of the DIMM are given in the JEDEC specification for the 168-pin 8-byte DRAM DIMM. The specification can be found by using the search string MO161 on the Electronics Industry Association's website at

http://www.jedec.org/DOWNLOAD/default.cfm

The electrical characteristics of the DIMM are given in section 4.5.6 of the JEDEC Standard 21-C, release 7. The specification can be found by using the search string JESD21-C on the Electronics Industry Association's website at

http://www.jedec.org/DOWNLOAD/default.cfm

### **ATA Interface**

ATA (AT Attachment) is a standard interface used with storage devices such as hard disk drives. For more information on ATA, refer to the following Apple website at

http://developer.apple.com/documentation/Hardware/DeviceManagers/ata/ata.html